AMDは昨年初め、RDNA 4フラッグシップRadeon RX 8900 XTXをキャンセルしたことが知られています。噂によると、Navi 4C GPUはTSMCのCoWoS技術を使用してパッケージ化された最大14個のチップレット(ダイ/タイル)を備えたモジュラー設計を特長としています。RX 8900 XTXは、CoWoS-Lシリコンブリッジを使用して接続された3つのActive Interposer Die AIDと1つのマルチメディアおよびI / Oダイ(MID)で構成されています。インターポーザダイは、C4バンプを使用して基板に接続されます。

マルチメディアおよびI/Oダイ(MID)は、Radeon RX 7900/7800シリーズGPUにあるMCD(Memory Complex Dies)と同じ役割を果たしました。これには、メモリコントローラ、対応するL3「Infinity Cache」、およびその他のI/Oデバイスが含まれます。

シェーダエンジンダイ(SED)は、3Dパッケージングを使用してアクティブインターポーザの上部に配置されます。各AIDには、CoWS-V TSVを使用して接続された3つのSEDがあります。完全に有効になったNavi 4C GPUは、最大9つのシェーダダイを備えており、RX 8900 XTXの場合、一部が無効になっています。これは、Instinct MI300と多くの共有ポイントを備えた驚くべきモジュラー設計でした。

しかし、トレーニング/推論ワークロードとは異なり、ゲームは待ち時間に非常に敏感です。AMDはInfinity Fabricクロックを増やし、Navi 31と32でMCDのレイテンシ問題を克服しました。複数のコンピューティングダイで同じことを行うことは、DRAMと高度なキャッシュ以上の機能を提供するため、非常に複雑です。9つの別々のシェーダーユニットを複数のチョークポイントと同期させることは、RX 8900 XTX(Navi 4C)を解決するための課題でした。

複雑なチップレットGPUアーキテクチャを説明するAMD特許

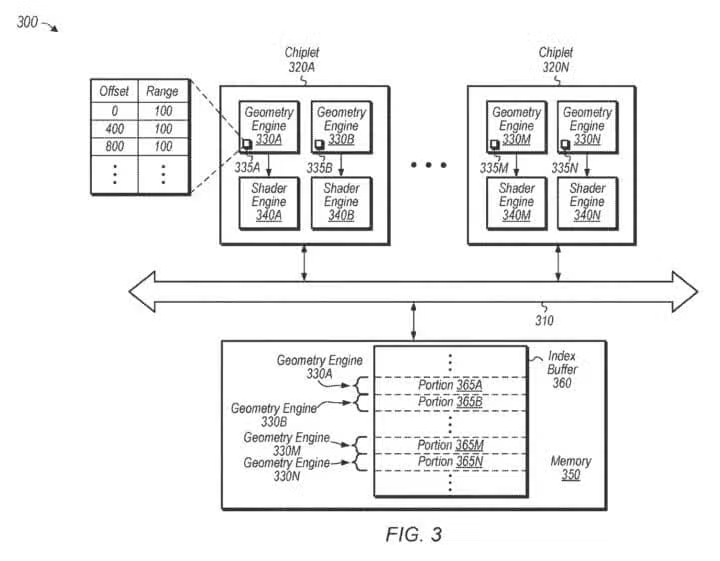

12月に、我々は非常に複雑なチップレットアーキテクチャの機能を説明するAMD特許を発見しました。この特許は、中央またはマスターダイなしで並列に動作する最大12個のダイからなる非常に柔軟なチップレットGPUアーキテクチャを説明しています。コマンドプロセッサ、ジオメトリエンジン、シェーダエンジン、ラスタライザなどの特殊ブロックで構成されたチップレット間の作業配布を細分化します。

各ダイは対応するインデックスを独立して実行します。ドローコールが実行されると、最初のジオメトリエンジンがインポートするインデックスバッファの一部を計算します。これは、ドローコールで作業しているジオメトリエンジンの数、ID、各部分にインポートするインデックスの数などに基づいて行うことができます。これにより、さまざまなジオメトリエンジンでローカルで独立してインデックスバッファの一部を並列に計算できます。

CPUはPCIeバスを介してメインメモリおよびGPUチップレットと通信します。チップレット自体はInfinity Fabricを使用して接続されています。CPU上で動作するアプリケーションは、チップレットを単一のエンティティと見なし、ファームウェアはチップレットを区別できる唯一のコンポーネントです。

この特許では、ジオメトリエンジン間でタスクを配布する方法について説明しています。そのうちの1つでは、デフォルトグループのサイズを使用して、部分ごとのインデックス数を決定します。サイズは基本タイプによって異なります。各ジオメトリエンジンはインデックスを計算して他のエンジンとは独立して処理するため、同期や障壁なしで並列実行が可能です。

下の図は、別々のジオメトリエンジンで3つの異なるストリップを描くことを示しています。網掛けされたプリミティブはインデックスのリセットのために削除され、破線で示された弧は巻き取り順序の方向を示します。インデックスリセットは、巻き取り順序の方向を反時計回りから時計回りに、またはその逆に反転させます。

別の方法は、分離されたチップレットの同期を含む。すべての描画呼び出しに対して、各コマンドプロセッサは、チップレットで実行される多数のパイプライン(処理ステップ)に対応するステータスIDを生成します。

チップレットGPU特許の多くは、ジオメトリエンジン(チップレット)間でインデックスを配布する方法を細分化しています。場合によっては、命令プロセッサは2つのパイプラインとペアになります。その結果、対応するジオメトリ、シェーダエンジン、およびラスタライザはそれぞれ1つのパイプラインに接続されます。同様に、残りのチップレットは2つのパイプラインで並列に動作します。

特許の残りの部分では、多数のチップレット間のドローコールとプリミティブ分割について議論しています。待ち時間ペナルティとキューの発散を最小限に抑えるように配置する必要があります。相互接続を介してデータを共有することなく、異なるダイのシェーダエンジンを適切に活用して同期する必要があります。

時間的な蓄積は、SLIとXFX(マルチGPU接続)の終わりを意味し、これらの問題が解決されない限り、チップレットGPUが出る可能性はほとんどありません。一見、私たちはチップレットGPUからまだ少なくとも2世代離れていると言いたいです。Radeon RX 8900 XTXがキャンセルされ、RDNA 4が予算とミッドレンジのモノリシックデザインとして残されたことが知られています。

Sorce: